Teil 2: Intels neue Core-Mikroarchitektur

- Intels neue Core-Mikroarchitektur

- Teil 2: Intels neue Core-Mikroarchitektur

- Teil 3: Intels neue Core-Mikroarchitektur

- Teil 4: Intels neue Core-Mikroarchitektur

- Teil 5: Intels neue Core-Mikroarchitektur

- Teil 6: Intels neue Core-Mikroarchitektur

- Teil 7: Intels neue Core-Mikroarchitektur

- Teil 8: Intels neue Core-Mikroarchitektur

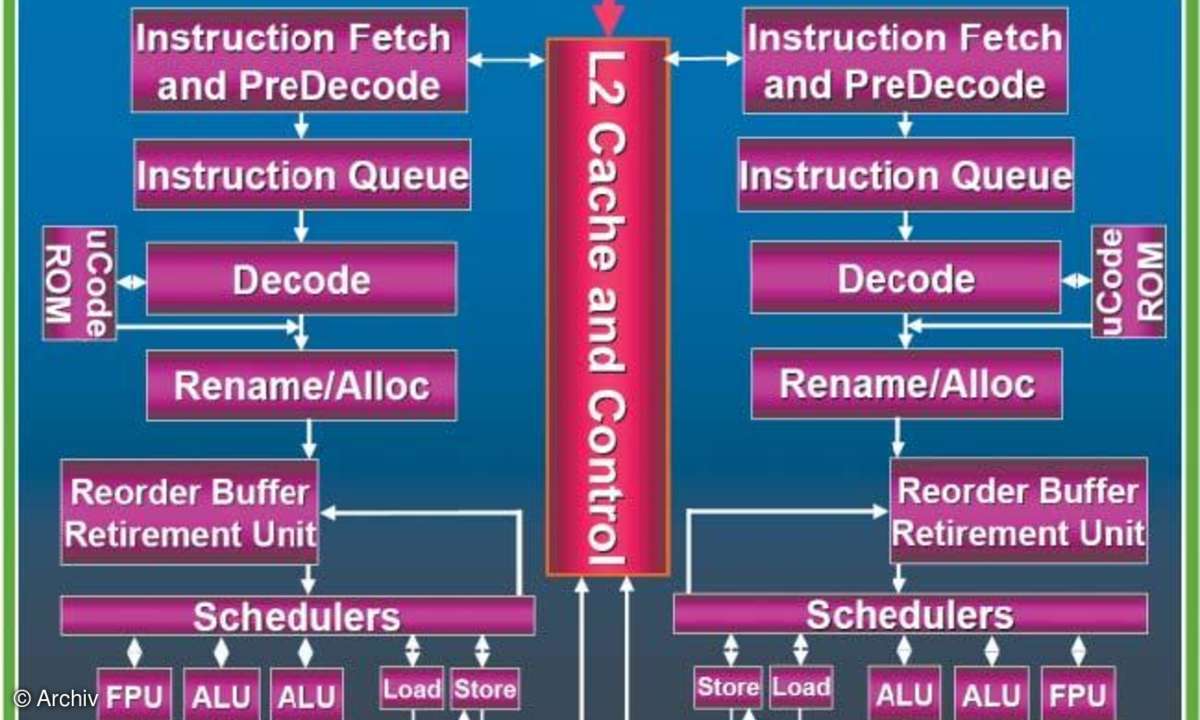

Frei nach dem Motto "viel hilft viel" hat Intel der neuen Architektur einen zusätzlichen "Simple Decoder" spendiert. Als zusätzlicher Decoder zu den bereits in der Yonah-Architektur enthaltenen beiden Simple und einen Complex Decoder soll die Verarbeitungsgeschwindigkeit bei optimaler Auslastung d...

Frei nach dem Motto "viel hilft viel" hat Intel der neuen Architektur einen zusätzlichen "Simple Decoder" spendiert. Als zusätzlicher Decoder zu den bereits in der Yonah-Architektur enthaltenen beiden Simple und einen Complex Decoder soll die Verarbeitungsgeschwindigkeit bei optimaler Auslastung der Decoder um 33 Prozent zulegen. Damit die Einheiten möglichst selten Däumchen drehen, wurde der Extended Stack Pointer (ESP) verbessert, der durch die Vorhersage wahrscheinlich benötigter Speicheradressen für ausreichend schnellen Nachschub sorgen soll.

Ein weiterer wichtiger Bestandteil der Wide Dynamic Execution ist die Macro Fusion, die die Anzahl der Micro-Ops in der Praxis um etwa 10 Prozent senken soll. Bei der Macro Fusion werden Befehle, die zusammenpassen, zu einer Micro-Operation verschmolzen.