Wireless & SuperSpeed USB, QuickPath/CSI, neues PCI Express und SATA

Wenn es um Geschwindigkeit bei PCs geht, denken die meisten Anwender an Prozessoren und Grafikkarten. Dass es die Schnittstellen und Busse sind, die den Prozessoren die Daten schnell genug heranschaffen müssen, wird oft vergessen. Eine ganze Reihe neuer Interfaces soll genug Leistung für die nächsten Jahre bringen.

- Wireless & SuperSpeed USB, QuickPath/CSI, neues PCI Express und SATA

- USB 3.0

- Wireless USB

- PCI Express 2.0

- SATA III / SATA 6 Gb/s

Dass hin und wieder neue Schnittstellen angekündigt oder erste Produkte vorgestellt werden, kommt alle Jahre wieder vor. Dieses Jahr aber kommt es richtig geballt: Intel stellt eine neue Prozessoranbindung vor, USB und SATA streiten sich darum, wer die schnellere Schnittstelle für Festplatten biet...

Dass hin und wieder neue Schnittstellen angekündigt oder erste Produkte vorgestellt werden, kommt alle Jahre wieder vor. Dieses Jahr aber kommt es richtig geballt: Intel stellt eine neue Prozessoranbindung vor, USB und SATA streiten sich darum, wer die schnellere Schnittstelle für Festplatten bietet, zudem steht die Einführung passender Karten für den Bus PCI Express 2.0 an, bevor PCI Express 3.0 neue Maßstäbe setzt. Was sich alles tut, haben wir für Sie zusammengefasst.

QuickPath/CSI

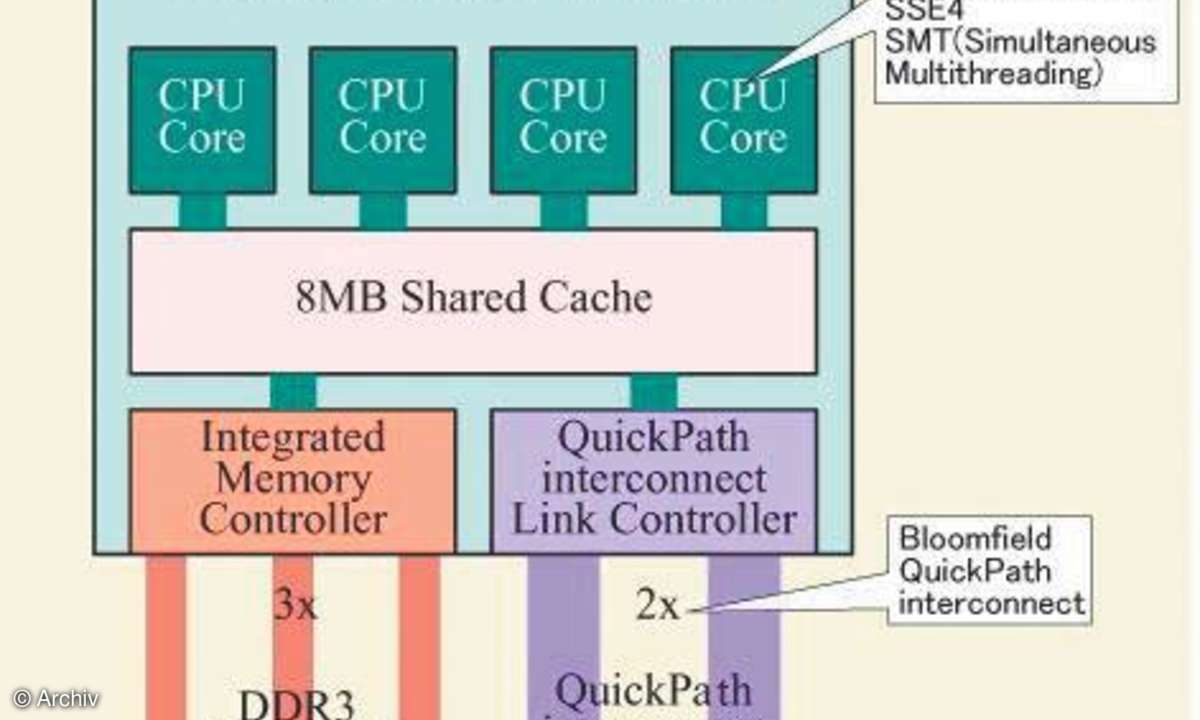

Mit dem CSI (Common System Interface) löst Intel dieses Jahr einen der ältesten Busse in aktuellen PCs ab -- den FSB (Front Side Bus). Diese Verbindung zwischen Prozessor und CPU wurde von Intel 1995 eingeführt und diente damals zur Anbindung eines oder -- und das war der eigentliche Hintergrund -- mehrerer Pentium-Pro-Prozessoren.

Mittlerweile ist der FSB nicht nur in die Jahre gekommen, sondern es hat sich auch gezeigt, dass er in vielen Bereichen nicht mehr konkurrenzfähig zu moderneren CPU-Schnittstellen wie etwa AMDs Hypertransport ist. Das liegt nicht nur an der Geschwindigkeit des FSB -- immerhin läuft die gerade aktuelle Version mit 400 MHz (als FSB 1600 vermarktet, da er vier Daten pro Takt überträgt).

Die Nachteile des FSB wiegen schwerer, sobald es um Speicherzugriffe eines, aber vor allem mehrerer Prozessoren geht. Bislang hat sich Intel mit teilweise gewaltigen L3-Caches von 16 und mehr MByte beholfen, die den FSB entlasten, über den die Speicherzugriffe ja laufen müssen. Chipsätze für Mehrprozessorsysteme wurden gar mit zwei FSBs ausgestattet, um den Engpass zu erweitern.

Für Maschinen mit mehreren CPUs reicht auch das nicht wirklich aus, da der FSB keine Mechanismen zur Wahrung der Cache-Kohärenz bietet. Die Abfrage, ob geteilte Daten gerade von einem anderen Prozessor bearbeitet werden und daher nicht zur Verfügung stehen, erfolgt bei Mehrprozessorsystemen ebenfalls über den schon ausgelasteten FSB.

Mit all diesen Nachteilen soll QuickPath Connect, wie der CSI von Intel auch genannt wird, aufräumen. Wie alle modernen Verbindungen ist auch der CSI im Grunde seriell ausgeführt. Das erlaubt eine gewisse Skalierbarkeit.

Ein CSI ist in voller Ausführung 20 Lanes breit, wobei jede Lane aus jeweils einem Paar Datenleitungen (differenzielle Übertragung) für Ein- und Ausgabe besteht. Im Gegensatz zum FSB kann der CSI also Daten im Vollduplex-Modus übertragen. Fünf solcher Lanes sind zu einem so genannten Quadranten zusammengefasst. Sind nicht alle Leitungen nötig, kann der CSI auch als Magerversion bestehend aus einem oder zwei Quadranten, also mit 5 oder 10 Lanes ausgeführt werden.

Jede Lane überträgt in den ersten Versionen des CSI laut Informationen des amerikanischen IT-Journalisten David Kanter Daten mit einer Transferrate von 4,8 oder 6,4 GBit/s. Das würde bedeuten, dass der CSI auf eine Bruttodatenrate von 12 bis 16 GByte/s käme. Netto sind es weniger, da die Daten in 80-Bit-Paketen verschickt werden, von denen aber nur jeweils 64 Bit Nutzdaten sind, während die übrigen 16 Bit als Steuerdaten verwendet werden.

Da es der FSB 1600 auf 12,8 GByte/s bringt (wenngleich nur unidirektional), ist bei ersten CSI-Schnittstellen eher vom schnelleren der beiden geschätzten Werte auszugehen. Einen wenn auch nur nominell langsameren Bus nachzuschieben, wird Intel vermutlich vermeiden.

Als Teilnehmer der vom CSI per Punkt-zu-Punkt-Verbindung zusammengeschalteten Geräte kommen nicht nur Prozessoren, sondern -- wie bei AMDs Hypertransport -- auch andere Chips in Frage.

Obwohl der CSI im Prinzip seriell konzipiert ist, überträgt er -- zumindest in den ersten Implementierungen -- die Daten parallel. Beim Hochfahren senden die Teilnehmer Testmuster, um die Leitungen zu prüfen und eventuelle Laufzeitdifferenzen zwischen den einzelnen Leitungen zu bestimmen. Steht die Verbindung, werden die Daten parallel übertragen.

Nur noch hin und wieder prüfen die CSI-Geräte, ob die gemessenen Latenzen der einzelnen Lanes noch stimmen. Spätestens beim Übergang von Kupfer zu optischen Leitungen wird der CSI dann wohl ohne große Änderungen als rein serieller Bus fungieren.

Bis zur Einführung des CSI dauert es nicht mehr lange. Intels nächste Prozessorgeneration mit dem Nehalem-Kern wird neben der neuen Schnittstelle auch gleich einen neuen Sockel bekommen, den LGA1366. Auch wenn der CSI weniger Leitungen benötigt als der FSB, werden mehr Pins nötig, da wie bei AMDs Prozessoren der Speichercontroller ebenfalls in den Prozessor verlagert wird.

Weiter geht's auf den folgenden Seiten mit SuperSpeed USB beziehungsweise USB 3.0, Wireless USB (WUSB), PCI Express 2.0 und 3.0 sowie SATA III alias SATA 6Gb/s.